| EP-212 Electronics Lab-2 : Analog Electronics |                          |               |              |                 |     | Page1/4 |

|-----------------------------------------------|--------------------------|---------------|--------------|-----------------|-----|---------|

| Name:                                         | Roll Number:             |               |              |                 | _   |         |

| Laboratory 6                                  | <b>A</b> : /7 <b>B</b> : | /3 <b>C</b> : | /6 <b>D:</b> | /4 <b>Tot</b> : | /20 |         |

# Instrumentation amplifier

Today's lab is a mini-quiz. You are allowed to discuss with your group for the design & analysis of Parts A to C – get your answers checked in sequence. Circuit building& testing happens in Part D.

The term 'instrumentation amplifier' is generally used to denote an amplifier that has the following properties:

- 1. High gain

- 2. Accepts a differential input

- 3. Has very high and symmetric input impedance

- 4. Produces a single ended output with reference to a user supplied  $V_{ref}$

- 5. Has very small output impedance

- 6. Has very high CMRR

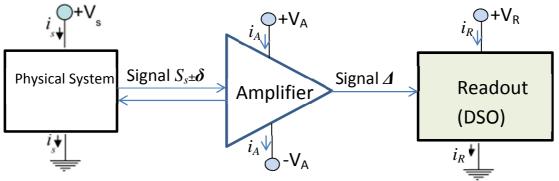

In this assignment we will build up an instrumentation amplifier in steps to satisfy each of the above criteria Recall the diagram of a measurement system shown in Fig 1, which we discussed in the introductory lecture:

Fig 1: Typical measurement system with an instrumentation amplifier

### Introduction – definition of CMRR

The steady state currents consumed by the three components: Source  $i_s$  Amplifier $i_A$  Readout  $i_R$  are usually very different. Hence the steady state signals generated by the three devices  $S_S S_A S_R$  will also be different. These can be voltage or current signals.

The source is a transducer that converts a physical effect (eg: light shining on a photo-diode, pressure measured by a piezo sensor etc...) into a small electrical signal  $\delta$  centered around the steady-state value  $S_{S}$ . For avoltage source:  $S_{S}$  is typically set to  $(V_{S}/_{2})$  so as to maximize the 'dynamic' range:  $S_{s}\pm\delta = V_{s'/_{2}}\pm\delta$  is allowed to swing the through the full range between  $V_{S}$  and 0. This places a restriction on the design of the amplifier with (large) gain G: The amplifier's output  $S_{A} = G^{*}(S_{s}\pm\delta)$  would normally be so large as to always keep  $S_{A}$  saturated.

Therefore the amplifier, which we now call an instrumentation amplifier, must operate such that the steady-state source signal  $S_s$  is rejected and only the dynamic part $\pm \delta$  is amplified:  $S_A = \pm \Delta = G^*(\pm \delta)$

This principle is called Common Mode Rejection, and it is quantified by the Common Mode Rejection Ratio (CMRR)

<u>Mathematical definition of CMRR</u>: Consider a two-terminal device which produces voltages  $V_1 V_2$  at its terminals. The signal input to the amplifier is $V_{in} = (V_1 - V_2)$ . An amplifier with differential signal gain  $A_D$  provides  $V_{out} = A_D V_{in}$  The common mode signal is defined as  $V_{cm} = (V_1 + V_2)/2$  and the common-mode gain is  $A_{CM} = V_{out}/V_{cm}$ . The CMRR is defined by the following formula. You want to have it as large as possible. The 'bare' opamp has an intrinsic CMRR (look this up in the datasheet). A feedback circuit to stabilize the gain will almost always reduce the CMRR.

$$CMRR = \frac{A_D}{A_{CM}} in \ dB : \left(20\log_{10}\frac{A_D}{A_{CM}}\right) dB$$

Intelligent circuit design is required to keep the CMRR as high as *practically* possible.

## Part A: Difference amplifier

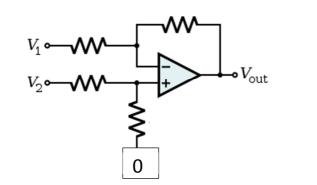

Consider the simple difference amplifier circuit in Fig 2(a). It has the two voltages  $v_1 v_2$  as input. To begin with let us consider  $v_1 \& v_2$  as two *independent voltages* – we are interested in what happens to the *difference*  $(v_1 - v_2)$

Fig 2(b): Difference amplifier – space for analysis

Fig 2(a): Difference amplifier – all resistors are of equal value R

**Q1:** What is the input impedance seen by  $v_1$  in Fig 2(a)?

**Q2:** What is the input impedance seen by  $v_2$  in Fig 2(a)?

**Q3:** Use KVL to determine the voltages at each node of the circuit in Fig 2(a) – mark your answers in the circuit of Fig 2(b)

Hint: Since the opamp draws no current, the voltages at its (+) and (-) terminal are always equal [Golden Rule 1 of opamp design!]

**Q4:** Using the answers to Q3, What is the relation of  $v_{out}$  to  $(v_1 - v_2)$ ? Hint: As discussed in the lecture, you can use superposition – set  $v_1$  and  $v_2$  to zero one at a time and determine  $v_{out}$

**Q5:**Suppose you have a common mode voltage  $v_{cm} = (v_1 + v_2)/2$  always present, what is the relation of  $v_{out}$  to  $v_{cm}$ ?

**Q6:** In the above calculations,  $v_{out}$  is referenced to the OVshown in Fig 2(a). Suppose OVis replaced by an arbitrary user defined voltage  $V_{ref}$  as shown in Fig 2(b). How does your answer to Q4 change? What is now the relation between  $v_{out}$  and  $v_1 - v_2$ ?

**Q7:** Basedon your answers to the above questions, list the criteria of the instrumentation amplifier design that a difference amplifer*doesnot* satisfy

| /1 |

|----|

| /1 |

/1

/1

/1

/1

# Part B: Evolution of the difference amplifier design

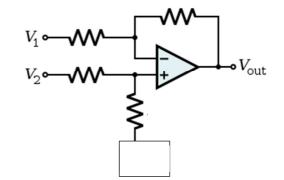

Let us work on improving the difference amplifier of Part A by fixing its problems one at a time:

**B**<sub>1</sub>: The most severe problem is obviously that the input impedance presented to  $V_{in}$  is small Add requisite blocks to the difference amplifier so that the input terminals  $v_1$  and  $v_2$  look into large (equal) impedances. Draw your modified block diagram here.

**B**<sub>2</sub>: The second obvious problem is the high gain requirement for the instrumentation amplifier, which we have not gotten out of the difference amplifier yet. Investigate ways of providing large gain to the *differential* signal  $v_d = (v_1 - v_2)$

Draw your possible design of a high gain, high input impedance differential amplifier here:

/0.5

**Important:** For whatever design you make here, calculate *both* the differential gain  $A_D$  and the commonmode gain  $A_{CM}$  of your design. Recall that our final objective is to make  $A_D$  very high while keeping  $A_{CM}$  as low as possible for high CMRR.

/2

#### /0.5

# Part C1: Final design of Instrumentation amplifier

By now, you should have solved most of the problems of the simple difference amplifier to arrive at a *nearly* good instrumentation amplifier. **Except** we still need to:

- 1. Minimize the common mode gain A<sub>cm</sub> to get a high CMRR

- 2. Reduce dependence on values of discrete passive parts like resistors. Ideally, the entire circuit should use just one value of the resistor R, and the gain must be set by one gain setting resistor  $R_q$

Make the requisite improvements to design of Part C to arrive at the final design of a 3 opamp instrumentation amplifier which satisfies all the 6 criteria listed on page 1.

Part C<sub>2</sub>: The CMRR – is it good?

Calculate the differential and common mode gains  $A_D$  and  $A_{CM}$  of your design Hint: Use Golden Rule 1 and superposition for  $A_D$ . Determine the quantity and directions of current flow with  $v_1=v_2$  for  $A_{cm}$

> /1: A<sub>D</sub> /2.5:A<sub>cm</sub>

/2.5

## Part D: Test of Instrumentation amplifier

Build and demonstrate the operation of your 3 opamp instrumentation amplifier designed in Part C. You may set G=10. Use a differential sine wave signal of small magnitude as  $V_{in}$  Demonstrate the high CMRR of your design by applying an offset to  $V_{in}$  and checking if the offset is rejected by the circuit.

Note that the three opamp instrumentation amplifier is often available as a pre-packaged IC (for example AD524). All the resistors are precision matched within the IC – only 2 external pins are provided to connect the gain setting resistor.

/4