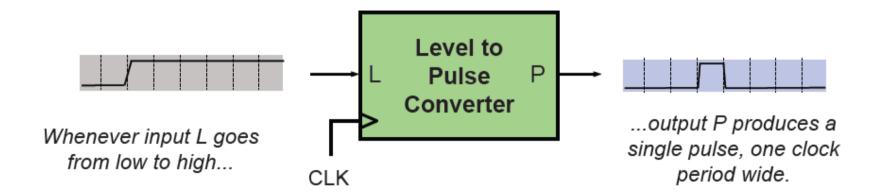

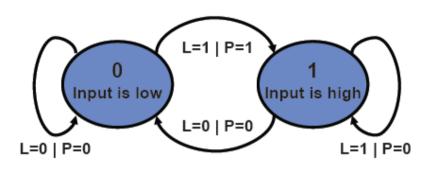

- A level-to-pulse converter produces a single-cycle pulse each time its input goes high.

- In other words, it's a synchronous risingedge detector.

- Sample uses:

- Buttons and switches pressed by humans for arbitrary periods of time

- □ Single-cycle enable signals for counters

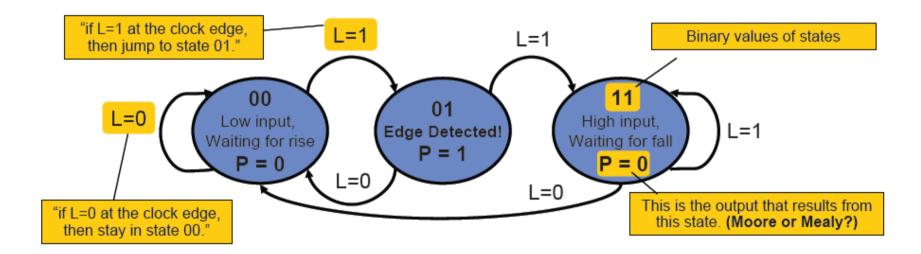

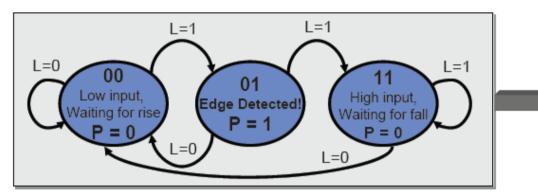

State transition diagram is a useful FSM representation and design aid

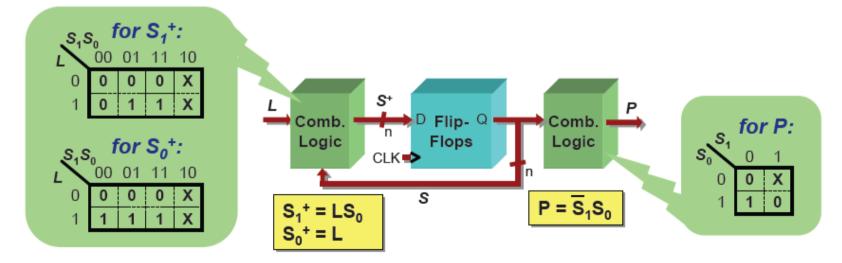

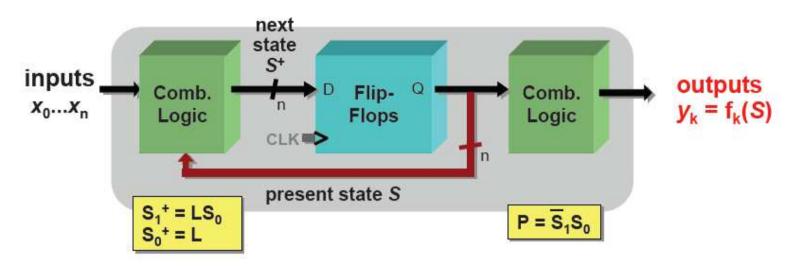

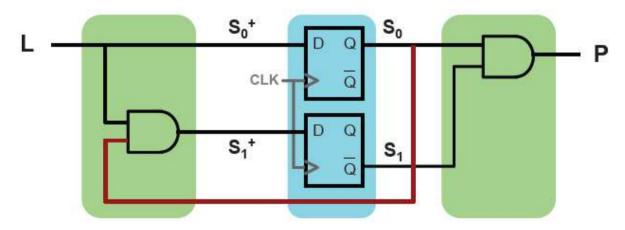

## **Logic Derivation for a Moore FSM**

Transition diagram is readily converted to a state transition table (just a truth table)

| Cur<br>Sta     | rent<br>ate | ln | Ne<br>Sta |             | Out |  |

|----------------|-------------|----|-----------|-------------|-----|--|

| S <sub>1</sub> | So          | L  | $S_1^+$   | $S_{o}^{+}$ | P   |  |

| 0              | 0           | 0  | 0         | 0           | 0   |  |

| 0              | 0           | 1  | 0         | 1           | 0   |  |

| 0              | 1           | 0  | 0         | 0           | 1   |  |

| 0              | 1           | 1  | 1         | 1           | 1   |  |

| 1              | 1           | 0  | 0         | 0           | 0   |  |

| 1              | 1           | 1  | 1         | 1           | 0   |  |

|                |             |    |           |             |     |  |

Combinational logic may be derived by Karnaugh maps

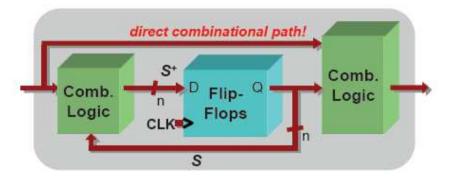

# **Moore Implementation**

Moore FSM circuit implementation of level-to-pulse converter:

Note: 3 states, so  $2^2 = 4 > 3$  i.e. 2 memory bits needed, with one unused state

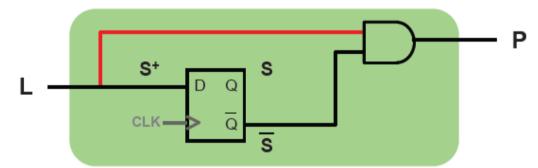

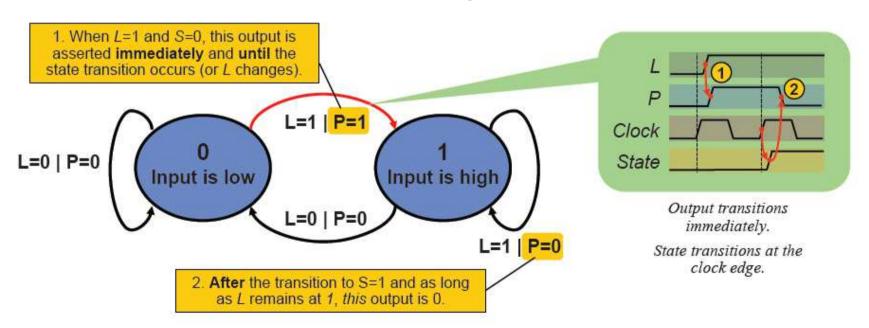

## **Mealy FSM Design**

| Pres.<br>State | In | Next<br>State  | Out |

|----------------|----|----------------|-----|

| S              | L  | S <sup>+</sup> | P   |

| 0              | 0  | 0              | 0   |

| 0              | 1  | 1              | 1   |

| 1              | 0  | 0              | 0   |

| 1              | 1  | 1              | 0   |

Mealy FSM circuit implementation of level-to-pulse converter:

- FSM's state simply remembers the previous value of L

- Circuit benefits from the Mealy FSM's implicit single-cycle assertion of outputs during state transitions

## **Mealy FSM implementation**

Since outputs are determined by state and inputs, Mealy FSMs may need fewer states than Moore FSM implementations

#### **Mealy/Moore FSM Trade-Offs**

- Remember that the difference is in the output:

- Moore outputs are based on state only

- ☐ Mealy outputs are based on state and input

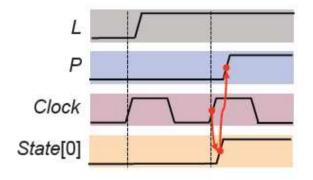

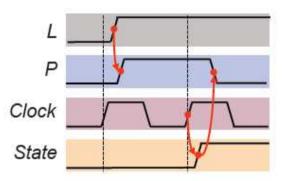

- □ Therefore, Mealy outputs generally occur one cycle earlier than a Moore:

Moore: delayed assertion of P

Mealy: immediate assertion of P

- Compared to a Moore FSM, a Mealy FSM might...

- □ Be more difficult to conceptualize and design

- □ Have fewer states